看似多余实则无用的金手指镀金引线对高速信号有影响吗?

发布时间:2023-08-14 14:07

首先简单说明下Chris为什么会写这一篇本来应该属于东哥讲的工艺知识的文章哈!这篇文章的诞生完全是出于一次偶然的交谈,这天Chris在饮水机旁装水,刚好看到隔离封装部门的同事小马哥也过来,他刚和某友商板厂开完会,估计是讨论了板厂做金手指这类型板子的时候关于镀金后的引线残留工艺能力,于是随口和Chris提了一嘴,说“不知道5mil到15mil的引线残留到底对信号的SI性能有没有影响啊!”的确,我们见到过很多加工出来后带引线残留的金手指板,但是之前的确没去量化过它的影响!

于是Chris毫不犹豫的答应小马哥,会抽空进行引线残留的研究,看看引线对信号有什么影响。当然,Chris心里面还是有数的,大概知道对多高速率的信号才有造成影响。1G,2G的信号当然问题不大了,比较引线的长度也就是10mil上下的量级。于是Chris把研究的对象放在了更高速的PCIE信号上面,原因有两种,一是PCIE的信号速率到达16Gbps到32Gbps(4.0和5.0协议),另外就是我们说的金手指基本上都是用于PCIE信号的传输,当然另外占很大比例的就是DDR的内存条了。于是毫不意外,我们研究的对象就锁定在了PCIE的信号。

什么,不太了解金手指的镀金工艺甚至为什么要镀金?这样的话可能需要大家先去看看东哥的文章或者直接骚扰他。Chris在这个场合就不展开了介绍工艺方面的问题了,免得说着说着文章字数多了,关键时候又要再戛然而止,只能等下周才有结论了哦!根据Chris和封装小马哥的进一步沟通,知道了某家板厂对金手指的工艺能力是这样的:

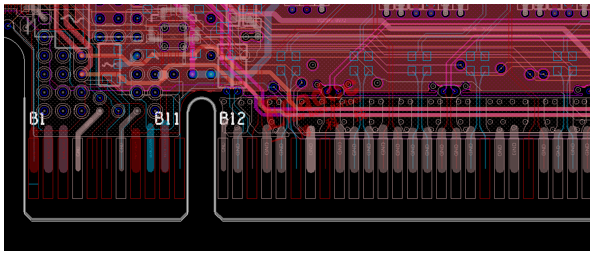

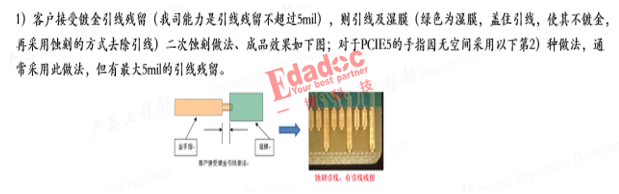

首先小马哥介绍了这家板厂的两种对金手指处理的工艺能力,一种引线残留在5mil左右,另一种是通过常规机械成型的方法,引线残留最大能到15mil。其中5mil内的引线工艺是通过干膜蚀刻的方法达到的,如下图所示。

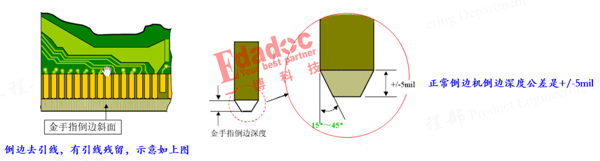

15mil的机械成型的方法就真的全靠物理加成了,是通过倒边的方法来实现!

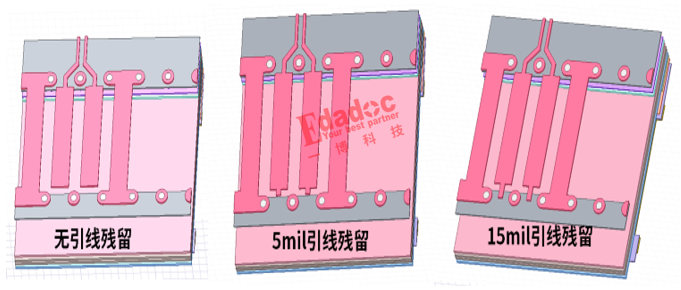

还是那句哈,大家如果对工艺实现本身感兴趣的话,就去找东哥问个明白。下面的都是Chris的高速仿真验证的时间了哈!当然上面都说到了这家板厂是去做传输PCIE5.0的金手指,那Chris就直接以5.0来进行研究了。说时迟那时快,Chris翻出了之前做过的一个PCIE5.0的金手指项目建好的模型,那么我们就去研究在理想没有引线残留、5mil引线残留,还有就是最恶劣的15mil引线残留下三种case对PCIE5.0信号的影响,建模如下所示:

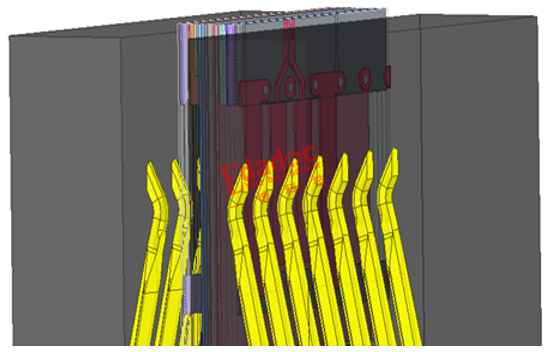

对,我们模拟出三种引线状态不同的case,那么我们下面就是要验证这三个金手指模型都插到PCIE的slot槽上的时候,去看他们各自性能的表现。对,就是下面这样的模型!

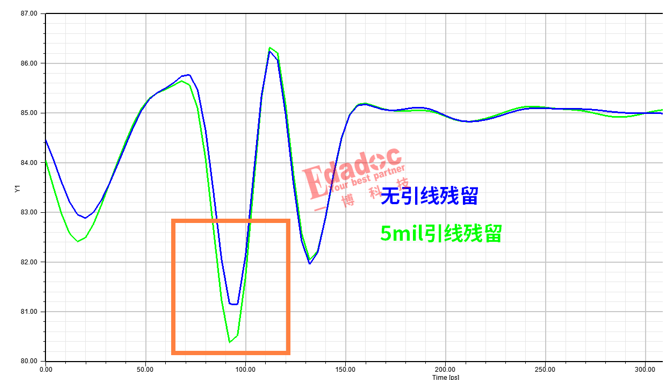

那么我们首先来看看没有引线残留的理想状态下和有5mil的引线残留两个模型插到slot后的TDR阻抗的对比情况,如下所示:

感觉还好啊,阻抗也就是降低1个欧姆左右,基本上没啥影响啊!看起来如果能做到5mil以内的引线残留的话,对信号质量的影响其实是可控的哈!

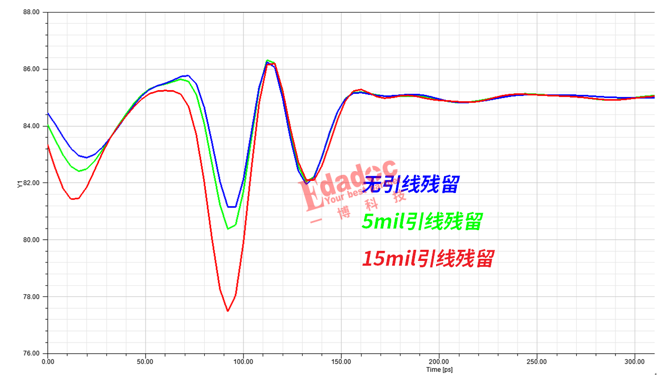

那如果引线残留有15mil呢,那我们再接着往下看哈,同样,我们仿真15mil的case3模型,然后把TDR阻抗的结果放到一起来进行对比,这样影响不就来了嘛!

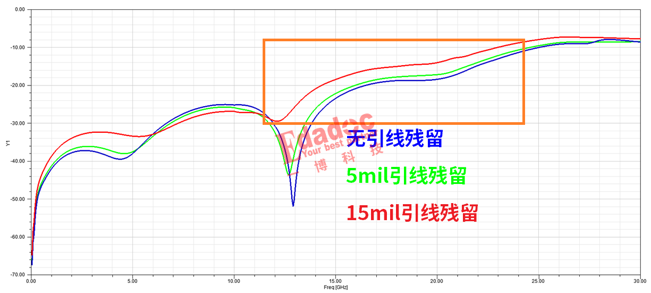

果然,15mil的引线残留影响就大很多了,阻抗比无引线残留的情况下要降低4-5欧姆,这是一个不少的量级了。这时候我们去看另外一个频域指标回波损耗的话,也能明显看到15mil引线残留的恶化。

简单总结下咯,看来金手指的镀金引线残留工艺也很有“先见之明”,工艺难度高的5mil内的引线残留的确对信号质量影响不大,但是去到工艺难度稍低的15mil内引线残留影响就真的不小了。对于我们SI来说,就是在设计中需要把这部分的影响考虑进去,在这个基础上来评估信号裕量是否足够了哈!