年少不知过孔好,分层起泡好烦恼

发布时间:2023-12-05 13:50

高速先生成员--王辉东

寒冬夜两点。

窗外雪满天。

有板要参展,

绘图不敢眠。

客户画板设计不容易,生产过程出问题,找到明明让她帮忙分析分析。

明明问客户出的啥问题,客户说焊接起泡层分离。

这个问题有点严重, 让我们大师兄今天来和大家一起说道说道。

爆板了,焊板是个什么东东。

爆板是PCB缺陷的一种,分为分层和起泡两种情况。

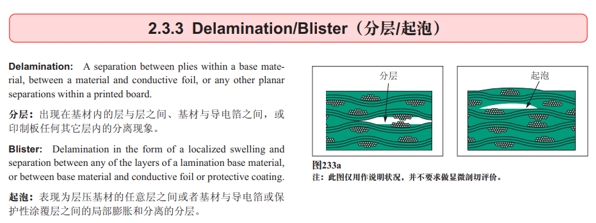

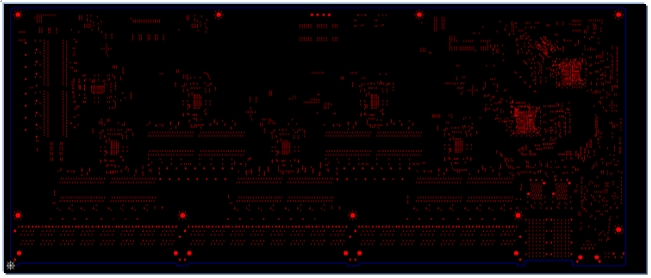

IPC-A-600H2.3.3里面有明确的规定,如下图所示:

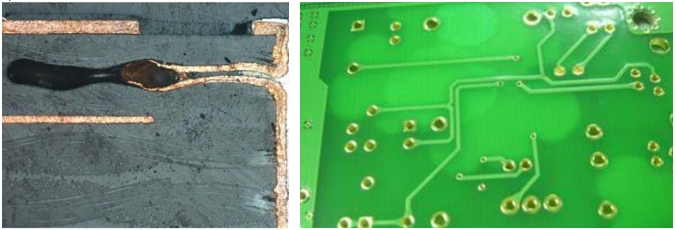

分层是在板子内部,正常是看不到的,起泡就像青春痘长脸上,大家都能看的到。

如果发生了爆板失效,则可以使用切片以及各种热分析手段来分析爆板原因,快速找到有效的应对措施。

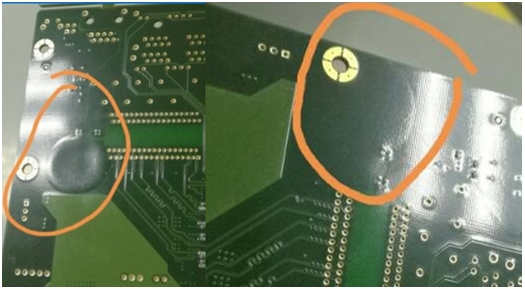

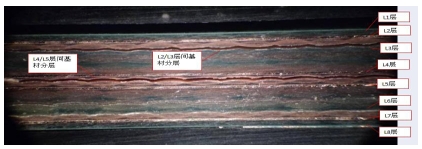

看看板子切片情况,层间分离,过孔稀少。

过孔在PCB中的作用是什么?

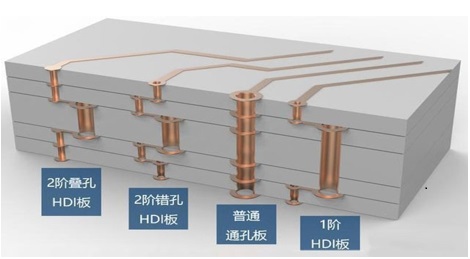

过孔(via)是PCB的重要组成部分之一,钻孔的费用通常占PCB制板总费用的30%或以上。简单的说来,PCB上的每一个孔都可以称之为过孔。从作用上看,

过孔可以分成两类:一是用作各层间的电气连接,就是导通和载流。二是用作器件的固定或定位。从导通的情况来看分为盲孔、埋孔和通孔。所谓的通孔,

就是这种孔贯穿过整个线路板,可用于实现内部互连或作为元件的安装定位孔。由于通孔在工艺上更易于实现,成本较低,所以绝大部分印刷电路板均使用

通孔。

从设计的角度来看,一个过孔主要由两个部分组成,一是中间的钻孔(drill hole),二是钻孔周围的焊盘区。这两部分的尺寸大小决定了过孔的大小。有客户

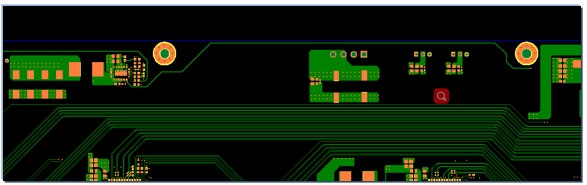

听板厂的业务说PCB上的过孔打的越少,价格越有优势。于是工程师就拼命的节约打孔,结果就有了下图这种情况。过孔分布很不均匀。

整个PCB过孔的分布情况

结果导致在焊接时,PCB受热膨胀,出现爆板的异常。

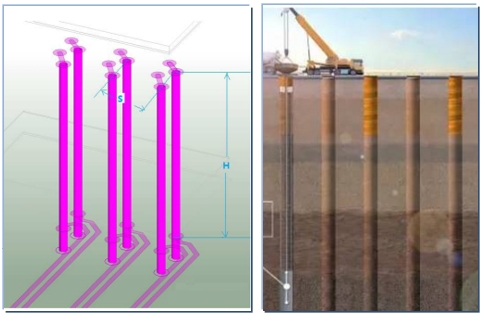

如果过孔设计分布均匀,钻孔和电镀完成后,过孔在线路上就像铆钉或者建筑工地的地桩,不但实现了导通还保证了强度支撑和牵引的作用。

过孔的均匀分布,有利于PCB散热,且起了一个加固作用,象一个个铆钉把PCB各层之间紧紧连接在一起。

那要具体怎么设置过孔呢

通常板内大面积空白区域,在不影响品质和信号质量的情况下可适当添加过孔。

当PCB尺寸在200mm以下,建议过孔间距设置为200mil,板子尺寸每增加100mm,过孔间距也相应增加100mil,防止分层起泡。

本期提问

关于PCB大面积空白区域,大家是否铺了地铜,加了孔,孔间距打多少,一起聊起来。