没开玩笑!高速信号不能参考电源网络这条规则,其实很难做到

发布时间:2024-05-28 10:24

高速先生成员--黄刚

看到这篇文章的题目,我相信大家心里都呈现出了这么一个场景:高速信号线在L20层,我只要把L19和L21层都铺上完整的地平面,这不就满足了高速信号线不能参考电源平面这条规则了吗?这难道很难做到吗?PCB的设计和叠层图都给你截出来了,只要叠层够,这一点都不难啊!

是的,高速信号线不能参考电源平面这一条规则是很容易满足的,但是大家再认真看看我们的题目是怎么说的?是“高速信号不能参考电源网络”。难道这两句话有区别吗?当然有,你们细细品味下,高速信号线不能参考电源平面其实指的只是高速链路中的差分线本身不能参考电源平面层,这是大多数工程师的理解。但是高速先生想说的是高速信号链路不仅仅只有走线,还有其他结构!

没错,高速先生想给大家说的是过孔结构!还是那句话,不让走线参考电源平面,在层数充裕的情况下一般都能做到。但是高速信号的过孔完全不参考电源过孔,这个就真的不容易了。大家又会说了,那我的高速信号过孔旁边都打地过孔,远离电源孔就好啦,不是也很容易做到吗,你确定所有的地方都能做到吗?

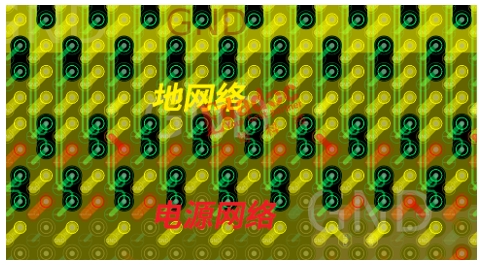

没错,例如在BGA的地方,真的就不是你说了算了!在一些大型的BGA,高速线的对数会比较多,从BGA的外圈一直延伸到BGA的内圈,然后内圈都存在着几种包括core电源在内的网络,也就是说,内圈的高速信号pin旁边极有可能存在着电源pin,那么有pin就有扇出,因此高速信号和电源的过孔基本上就无可避免的挨在一起了。

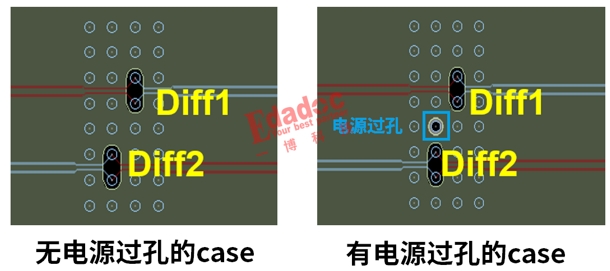

高速先生从来都不是只抛出问题的主,既然无法避开,只能接受,尝试分析这种情况下到底对高速信号有什么影响。于是二话不说,高速先生就做了一些简单但是能很好说明问题的测试板,去分析高速信号孔旁边有电源孔对无源的影响。我们设计的测试DUT如下所示:

简单的模拟一个1mm的BGA小阵列,上面各有两对高速信号通过过孔连接,两个case的区别为全是地过孔和有一个电源过孔在这个BGA小阵列里面。

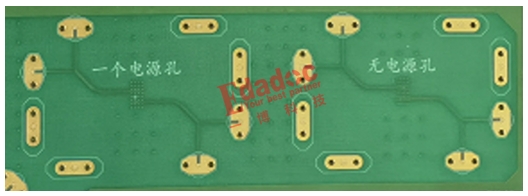

做出来的实物板就是这个样子了!

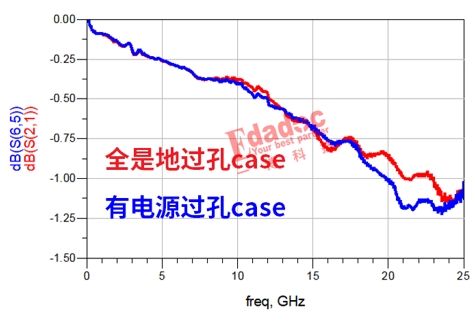

那我们通过网络分析仪进行测试,看看两种case下的无源性能的差异。

首先我们来看看DIFF1,也就是靠上的那一对,这一对相对DIFF2来说,地过孔保护得更好一点,我们来看看这一对的插入损耗的对比。

可以看到,DIFF1这对走线在两种case下的差异其实不大,也就是到了比较高频的时候(15GHz)才有一些差异,整体性能都是没问题的。

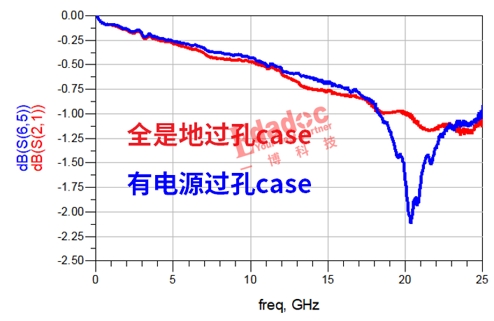

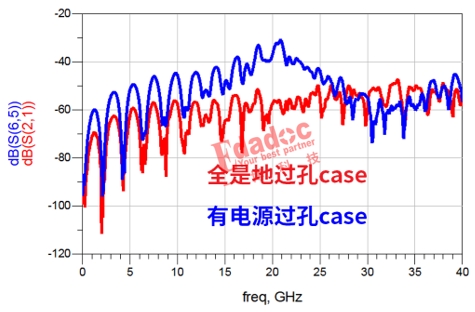

那重点来了,我们来看看被地过孔保护的没那么好的DIFF2,尤其是有电源过孔在旁边的这对信号,到底性能的差异是怎么样的呢?结果如下所示:

全是地过孔下的DIFF2当然没问题了,但是能看到,有电源过孔在旁边之后,这对DIFF2在20GHz有一些比较严重的谐振点,对信号质量来说当然是一种伤害了。也说明了DIFF2这对信号的的确确都参考到了这个电源过孔,性能随之被影响到。

其实被影响到的不仅仅是信号质量本身,我们来看看两种case下DIFF1和2之间的串扰,也能够发现明显的差异。能看到在插损被影响到的这个频段,串扰的恶化也是非常的严重,基本上串扰的量级差超过了20db。

最后再总结下本文的核心内容哈,这篇文章其实主要是让大家了解下除了PCB走线参考电源平面的影响巨大之外,在比较高的频段下,高速过孔旁边要是有电源过孔的话,同样也会有影响。只不过频段都去到了15GHz之后,没做到这个频率的产品的朋友们,也不用太过担心。不过话又说回来,这个频段其实也有很多产品涉及到了,因此根据具体设计的不同,也会给大家的产品带来一定的风险。虽然看起来在BGA区域,高速信号pin和电源pin挨着的事实无法改变,但是并不意味着我们就完全没有改善的方法。相信只要大家发现了问题,也就一定会想出办法去解决的哈!

问题来了:

面对BGA里面电源pin相邻的现实,大家能想到什么方法来改善它对高速信号的影响呢?