客户有哪些封装案例,一句克服使用让PCBA工厂泪流满面

发布时间:2024-06-25 11:56

客户一句克服使用让PCBA工厂泪流满面,今天我们一起来盘点盘点客户那些特殊的PCB设计和封装建立,你都是否有经历过,或者正准备这么做。

#PCB #PCBA #过孔 #DFM #PCB设计 #元器件

作者 | 高速先生成员--王辉东

天空下着雨,萧萧从窗前经过,看窗里。

翠萍那娇艳欲滴的脸上挂着两串泪滴。

萧萧一进去,问啥情况。

翠萍往电脑屏幕一指。

当萧萧看向屏幕一瞬间。

那些曾经以为早已遗忘的伤痛,会在某些时刻如潮水般涌来,让她猝不及防。

饶萧萧说客户的一句克服使用,让我泪流满面。

PCB 封装是什么

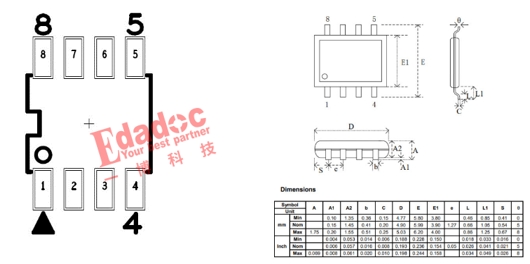

定义电子元器件和 PCB 之间的物理接口,为 PCB 组装生产和后期维修提供必要的信息。例如,元器件件的形状和符号,焊盘尺寸大小和数量、器件位置、1pin参考引脚、极性方向等。

也就是说将各种电子元器件的引脚、外形用图形形式画出来,用于画PCB的基础信息。

一个封装所包含的信息有:焊盘、丝印外形、装配外形、高度信息、MARK等一些辅助信息。

封装设计注意点有哪些:

PCB LAYOUT的便利性

满足各种工艺要求(制板、焊接)

装配的参考性

美观性

放置在 PCB 上的每个器件都是独一无二,都必须有自己的独立封装。

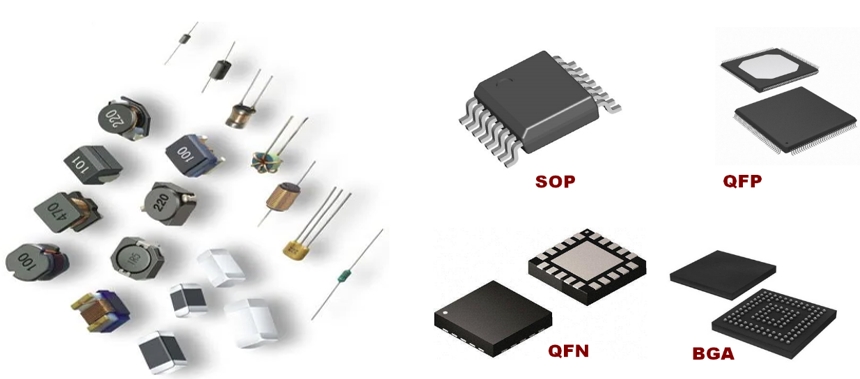

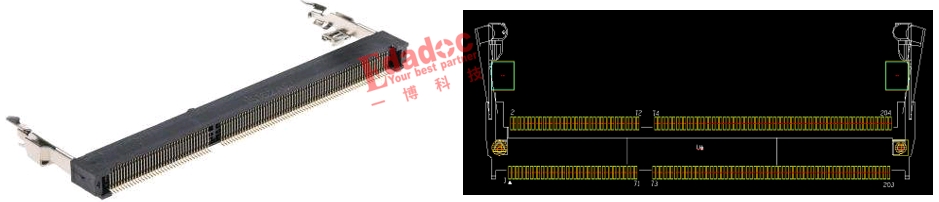

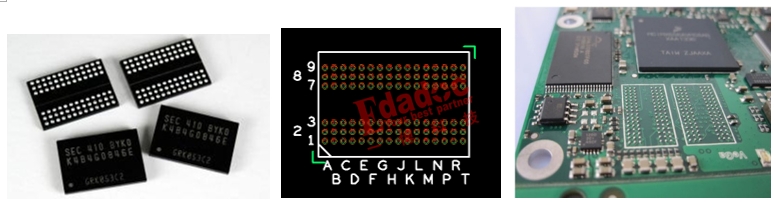

PCB常用的封装有哪些:

常用阻容感 、SOP(小外形封装)、QFP(四方扁平封装)、BGA(球栅阵列)、DIP插件等。

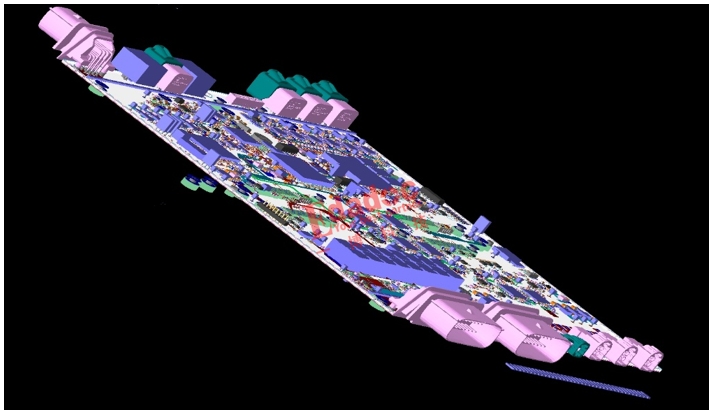

封装的3D图

封装的建立要依据data sheet,结合实际生产工艺进行优化建立。

实物封装和PCBA图

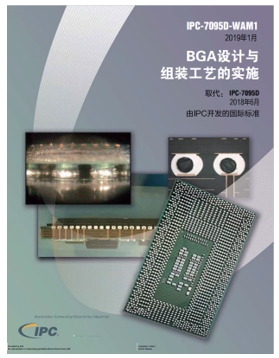

封装常用的IPC标准有哪些:

IPC-SM-782A 表面安装设计和焊盘设计标准

IPC-7351B 表面安装器件和焊盘图形标准通用要求

IPC-7095D BGA 设计与组装工艺的实施(这个专门为BGA设计生产而定制的标准)

PCB封装设计的那些DFM案例

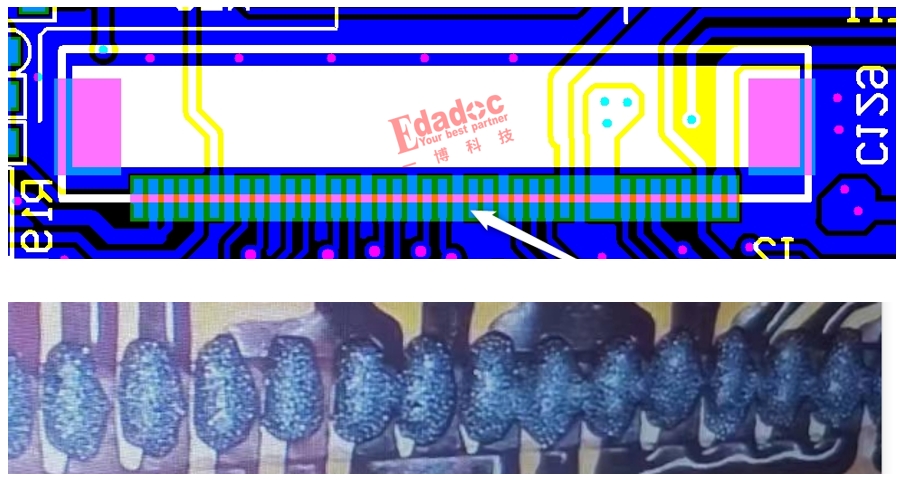

1. 焊盘尺寸与实物严重不符。如果焊接厂管控不好,很有可能这器件能从南极洲漂移到北冰洋去。

2.焊盘间距

焊盘的间距大小必满足PCB裸板的生产,比如要求保证器件焊盘间的阻焊桥。焊盘间距通常设计在7mil及以上,务必保证绿油桥的工艺能力。器件开通窗,没有阻焊桥阻挡,连锡短路。

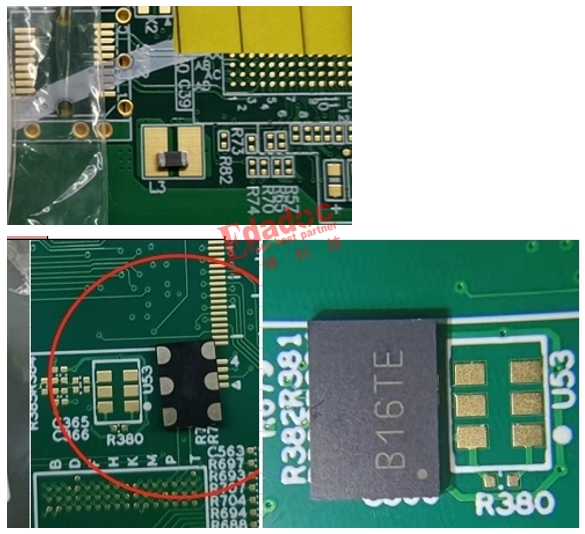

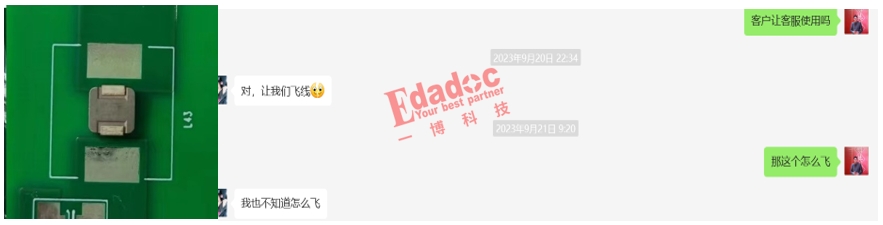

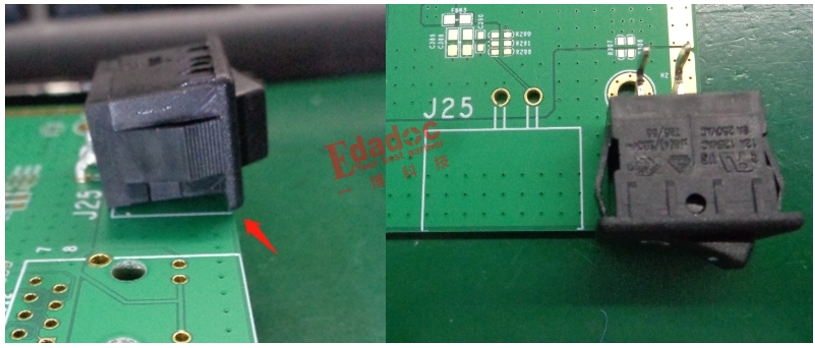

3.焊盘之间的内距过大,客户让克服使用,帮忙飞根线,你说这种工艺能实现吗?

4. 做装配最怕什么,板子安装完成了,核对BOM还有器件没有用完,这不还剩几颗固定螺丝。客户说我设计的孔在丝印层,害怕工厂生产漏掉,还特意在PCB上画了螺丝的符号,工厂说

你看我PCB裸板上是不是也有个丝印框,并且螺丝的符号也印的很清晰。

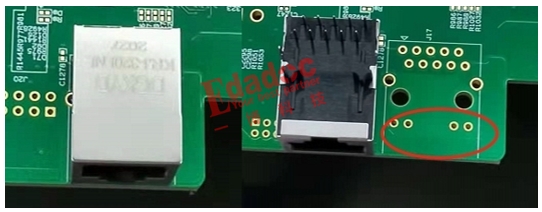

5.星星点灯,都唱了好多年,星星都能把灯点亮,而我却不能把网口的灯点亮。这个我来焊接,只能让客户克服使用了。

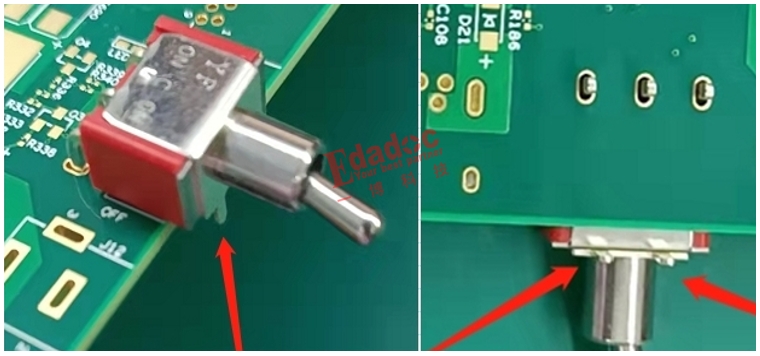

6.开关器件下沉不了,客户让克服使用,客户让引脚整形,给用力的掰出板外去,我没有这么大的力,客户净给我们出世界难题。我是汉族美女,不是女族汉子。

7.通孔元件,通孔设计的放置必须准确,以确保元件正确对齐和牢固连接。这个开关的固定脚伸出板外,客户让我克服使用,现在我们只好找剪刀把外面的脚剪掉。

8.板上成品孔封装设计太小,方形引脚插不进去,客户让我用力,用力插进去,有些东西,不是用力就能解决问题的,瞬间感觉大锤砸,小锤敲,路边摊上把火烧,这是PCBA焊接厂,

不是开铁匠铺。

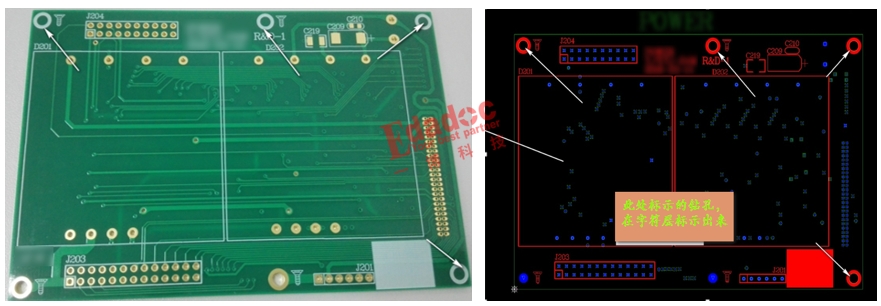

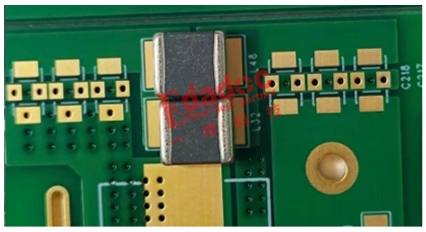

9.封装尺寸的大小,封装的建立是与器件本体1:1,还是比器件本体大,这些都会影响后面的布局。如下图的封装建立比器件本体小,导致布局时器件冲突。

饶萧萧说翠萍坚强点,擦干眼泪,不要哭泣,告诉你一个好消息。

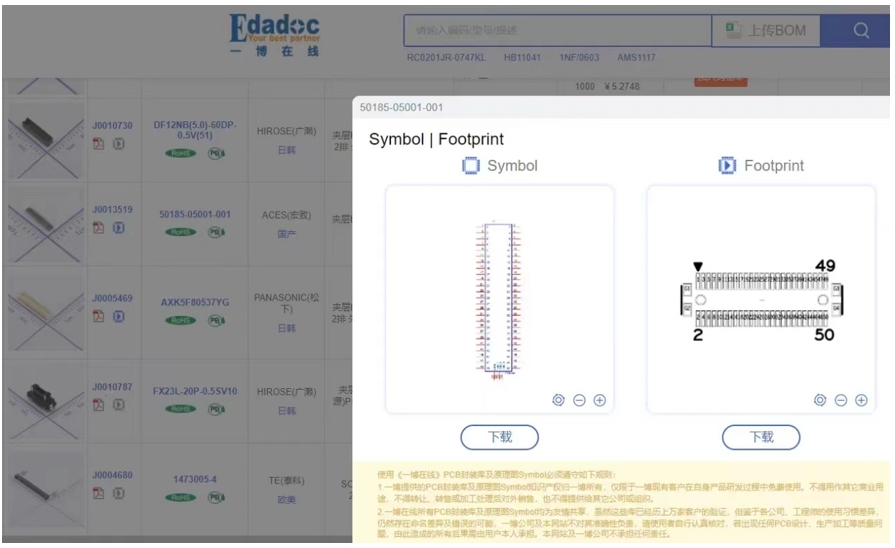

经过21年的沉淀积累,30多名工程师的辛勤付出,7000多天的奋战结果,千呼万唤,她终于来和大家见面了,一博在线元器件PCB封装库、原理图库正式面向所有用户开放,所有

一博在线注册用户均可免费下载。

请务必记住.cn平台共享,免费下载;需要账号的请联系我司对应销售或在此留言。

网站所有封装,免费下载,PCB硬件工程师的春天来了。