ODT在手,DDR5布线可以任性走?

发布时间:2022-12-27 12:56

作者:一博科技高速先生成员 姜杰

ODT是On Die Termination的缩写,又叫片内端接,顾名思义,就是把端接电阻放在了芯片内部。作为一种端接,ODT可以减小反射,对信号质量的改善显而易见,SI攻城狮很喜欢;作为一种片内端接,由于去掉了PCB上的终端电阻,大大的简化了设计,Layout攻城狮很钟意;作为一种可以灵活配置的片内端接,硬件攻城狮也爱不释手。总而言之,喜大普奔。

早在DDR2时代,数据信号就有了ODT功能,随着信号速率的提升和负载数量的增加,大家发现地址、控制和时钟(简称CAC)信号更需要这个功能,于是,又都在期待CAC信号的ODT功能什么时候能安排上,这一等就等了三代。

终于,DDR5 CAC信号的ODT闪亮登场!

我猜最激动还是Layout攻城狮:DDR5的CAC信号有了ODT功能,PCB布线约束可以放宽松了吗?毕竟,哪里信号质量差就可以端接哪里,So easy。

带着这个问题,开始我们今天的研究。先熟悉一下仿真对象:DDR5地址信号,走线为Flyby拓扑,一驱五,信号速率2800Mbps。

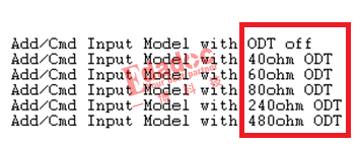

ODT的设置选项如下,分别是ODT off、40欧姆ODT、60欧姆ODT、80欧姆ODT、240欧姆ODT和480欧姆ODT。

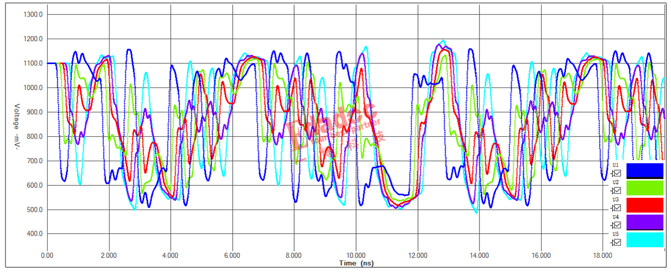

不管是否心存侥幸,还是先看看没有端接(ODT off)的地址信号波形(按照DDR由近及远的顺序,器件位号依次是U1、U2、U3、U4、U5):

不出所料,信号质量果然差。为了看的更清楚,我们把近端U1的信号波形和眼图单独拿出来,简直差到没眼看。

是时候展示ODT的作用了,既然所有的DDR信号质量都这么差,那就上点狠活,把所有的DDR都配置40欧姆ODT,让我们拭目以待。

哦豁,除了近端的两个DDR信号质量改善较大,其它DDR的信号质量似乎并未达到预期的效果。高速先生陷入了沉思,难道是ODT阻值选择有问题?试试所有ODT均为480欧姆。

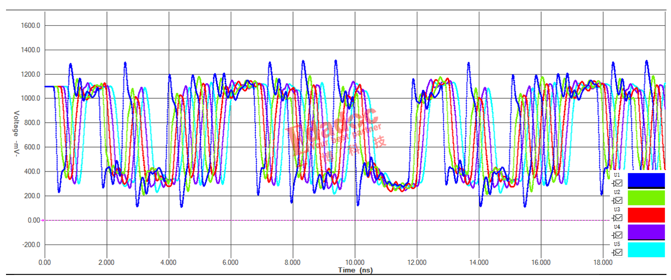

不行,再试试ODT从U1到U5逐个递增,依次为ODT40\ODT60\ODT80\ODT240\ODT480

还是不行,再试试ODT从U1到U5逐个递减,依次ODT480\ODT240\ODT80\ODT60\ODT40

信号有优化,但还是不理想。回到我们熟悉的老套路,仅末端的U5设置ODT40,同时,其它DDR选择ODT off。可以发现,各DDR的信号质量均有较大的改善,也都能满足协议要求了。

看到这里,对于DDR5的CAC信号能否任性走线的问题,想必大家都已经有了判断:答案是否定的。ODT确实可以改善信号质量,但不是万能的。正所谓随心所欲不逾矩,该遵守的布线规则还是要老实遵守,毕竟,DDR5的CA信号速率已经到了3200Mbps,甚至有可能更高,更何况还要应对一驱多的复杂拓扑。

问题来了

本案例中的一驱五DDR地址信号,为何每个颗粒都设置了端接的信号质量,反倒不如仅设置末端端接的好?