新闻动态

NEWS

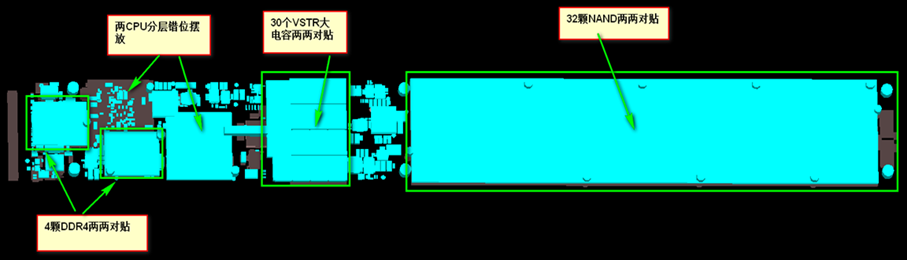

EDSFF单板设计案例

发布时间:2023-07-05 16:57

类别 | EDSFF(Enterprise &Datacenter Storage Form Factor) |

产品所属行业 | 存储 |

主要芯片 | CPU:CNX-2660_2670-AA DDR4:DDR4_SDP_DDP_BGA78_BGA78_0808_1 NAND:NAND_2CH_BGA152

|

单板类型 | SSD |

Pin数 | 8564 |

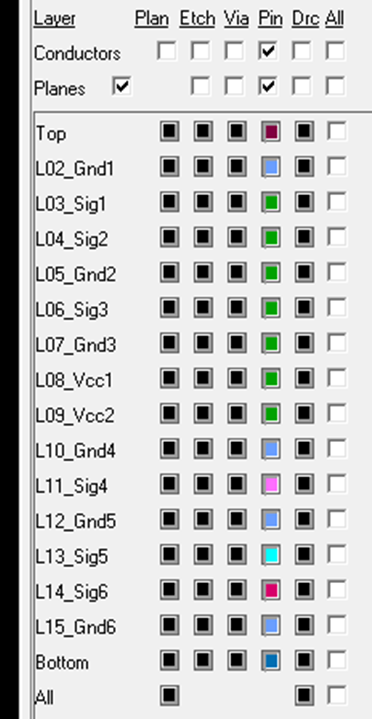

层数 | 16 |

最高信号速率 | 8Gb/s |

难点 | 1、 布局较密(Pin Density(pins/sq in)达260),双CPU,每个CPU各带2片DDR4颗粒和16片NAND,且客户希望尽量多的增加VSTR大电容的个数; 2、 板框为长条形的,布局布线空间受限;板厚限制为1.57mm,布线需求要做到16层,层叠设计比较极限; 3、 多方沟通(客户,板厂,公司内部),且有语言差异; |

我司对策 | 1、尝试不同方案的布局,通孔设计或者盲埋孔设计等,并与客户、工厂多方沟通,最终确定: Ø 通孔设计,减少成本; Ø BGA不考虑预留返修区; Ø 2个CPU放在不同层面错开摆放; Ø 所有VSTR大电容、DDR颗粒和NAND颗粒两两对贴摆放;

2、考虑单板的走线和电源(双CPU,每个CPU各带2片DDR4颗粒和16片NAND),因单板空间限制,需要6个走线层和2个电源层;板厚1.57mm,考虑单板和信号线的参考平面,通过和板厂沟通,最终确定16层,6个内层走线的层叠。这个层叠的不足之处为层间距比较小,走线线宽较细,且存在相邻层,对信号质量会有一定影响,增加布线难度。

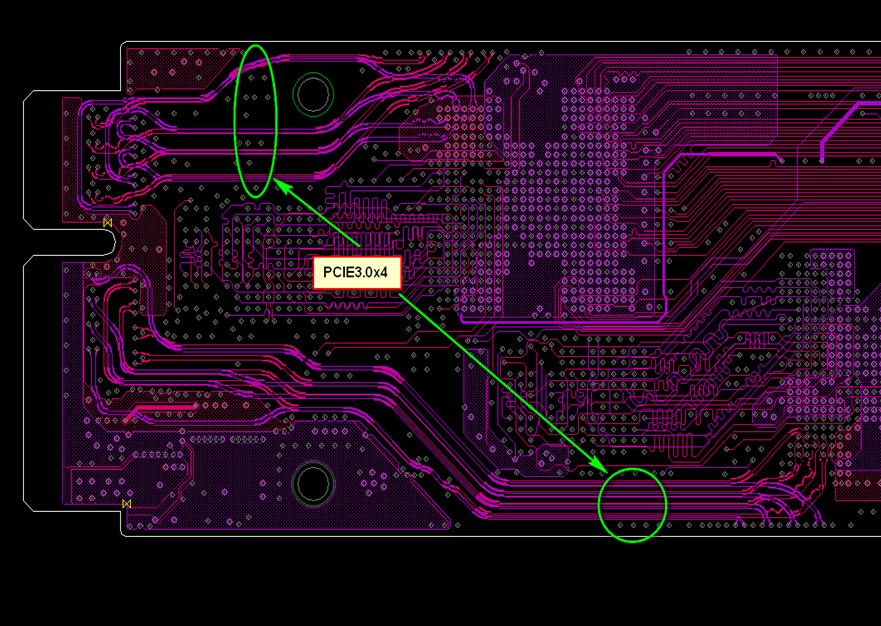

3、增加沟通效率: Ø 除常规的电话、邮件沟通外,重要节点、问题点安排工程师与客户现场的沟通,做到沟通及时、有效; Ø 与板厂的配合由之前通过客户和板厂沟通相关问题、然后把结果转达给设计工程师这种中转的方式,改为设计工程师直接和板厂方面沟通,同样有效的提升沟通效率,助力项目顺利开展; Ø SI人员参与,对重要信号进行仿真和优化,并对PCIE信号做背钻处理,提升信号质量;

|